목차

1. 스위칭 전원 공급 장치의 회로 구성

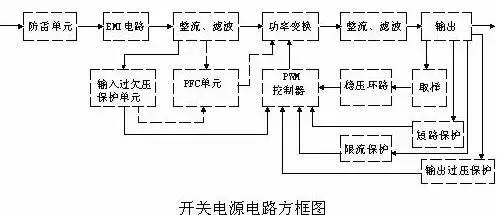

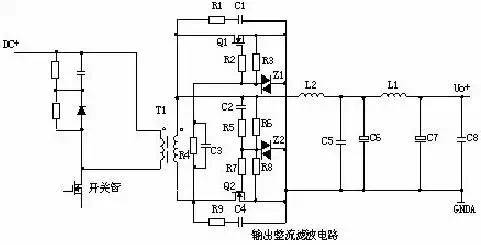

스위칭 전원 공급 장치의 주 회로는 입력 전자기 간섭 필터(EMI), 정류기 필터 회로, 전력 변환 회로, PWM 컨트롤러 회로 및 출력 정류기 필터 회로로 구성됩니다. 보조 회로에는 입력 과부족 전압 보호 회로, 출력 과부족 전압 보호 회로, 출력 과전류 보호 회로, 출력 단락 보호 회로 등이 포함됩니다.

스위칭 전원 공급 장치의 회로 구성도는 다음과 같습니다:

2. 입력 회로의 원리 및 공통 회로

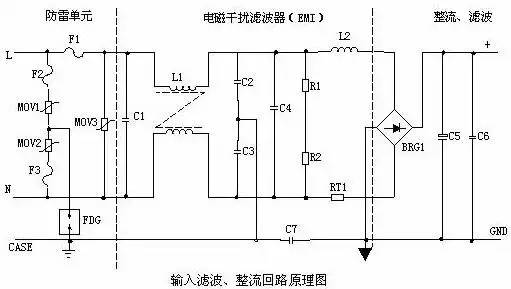

2.1 AC 입력 정류기 필터 회로 원리:

①. 낙뢰 보호 회로: 낙뢰가 발생하여 고전압이 발생하여 전력망을 통해 전원 공급 장치에 유입되면 MOV1, MOV2, MOV3 : F1, F2, F3 및 FDG1로 구성된 회로가 보호 기능을 제공합니다. 배리스터의 양단에 인가되는 전압이 작동 전압을 초과하면 저항이 감소하여 배리스터에서 고전압 에너지가 소비됩니다. 전류가 너무 크면 F1, F2, F3이 보호 회로를 소손시킵니다.

②. 입력 필터 회로: C1, L1, C2, C3로 구성된 이중 π 필터 네트워크는 주로 입력 전원 공급 장치의 전자기 노이즈와 클러터 신호를 억제하여 전원 공급 장치와의 간섭을 방지하고 전원 공급 장치 자체에서 발생하는 고주파 노이즈도 방지합니다. 전력망에 대한 전파 간섭. 전원이 켜지면 C5를 충전해야 합니다. 순간 전류가 크기 때문에 RT1(서미스터)을 추가하면 서지 전류를 효과적으로 방지할 수 있습니다. 모든 순간 에너지가 RT1 저항에서 소비되므로 일정 시간 후 온도가 상승하면 RT1의 저항이 감소합니다(RT1은 음의 온도 계수 성분). 이때 소비되는 에너지는 매우 적으며 후속 회로가 정상적으로 작동할 수 있습니다.

③. 정류기 및 필터 회로: AC 전압이 BRG1에 의해 정류된 후 C5에 의해 필터링되어 비교적 순수한 DC 전압을 얻습니다. C5의 용량이 작아지면 출력 AC 리플이 증가합니다.

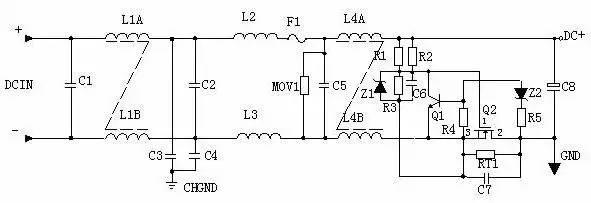

2.2 DC 입력 필터 회로 원리:

①. 입력 필터 회로: C1, L1, C2로 구성된 이중 π 필터 네트워크는 주로 입력 전원 공급 장치의 전자기 노이즈와 클러터 신호를 억제하여 전원 공급 장치와의 간섭을 방지합니다. 또한 전원 공급 장치 자체에서 생성되는 고주파 잡음이 전원 공급 장치에 영향을 미치는 것을 방지합니다. 그리드 간섭. C3 및 C4는 안전 커패시터이고 L2 및 L3는 차동 모드 인덕터입니다.

②, R1, R2, R3, Z1, C6, Q1, Z2, R4, R5, Q2, RT1 및 C7이 서지 방지 회로를 형성합니다. 시작 시에는 C6의 존재로 인해 Q2가 전도되지 않고 전류가 RT1을 통해 루프를 형성합니다. Q2는 C6의 전압이 Z1의 조정된 값으로 충전되면 켜집니다. C8이 누설되거나 다운스트림 회로가 단락되면 RT1의 전류에 의해 생성된 전압 강하가 시작되는 순간 증가합니다. Q1이 켜지고 Q2는 게이트 전압 없이 전도되지 않습니다. RT1은 단시간에 소손됩니다. 다운스트림 회로를 보호하세요.

3. 전력 변환 회로

3.1 MOS 튜브의 작동 원리:

현재 가장 널리 사용되는 절연 게이트 전계 효과 튜브는 반도체 표면의 전기 음향 효과를 사용하여 작동하는 MOSFET(MOS 튜브)입니다. 표면 전계 효과 장치라고도 합니다. 게이트가 비전도성 상태이기 때문에 입력 저항을 최대 105옴까지 크게 높일 수 있습니다. MOS 튜브는 게이트-소스 전압을 사용하여 반도체 표면에 유도된 전하의 양을 변화시켜 드레인 전류를 제어합니다.

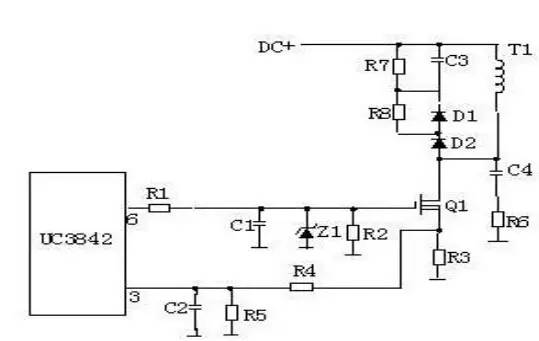

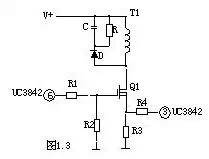

3.2. 일반적인 회로도:

3.3. 작동 원리:

R4, C3, R5, R6, C4, D1 및 D2는 버퍼를 형성하고 스위치 MOS 튜브와 병렬로 연결되어 스위치 튜브의 전압 스트레스를 줄이고 EMI를 줄이며 2차 고장을 방지합니다. 스위치 Q1이 꺼지면 변압기의 1차 코일은 피크 전압과 피크 전류를 생성하기 쉽습니다. 이러한 구성 요소의 조합은 피크 전압과 전류를 잘 흡수할 수 있습니다. R3에서 측정된 전류 피크 신호는 현재 작업 사이클의 듀티 사이클 제어에 참여하므로 현재 작업 사이클의 전류 제한이 됩니다. R5의 전압이 1V에 도달하면 UC3842가 작동을 멈추고 스위치 Q1이 즉시 꺼집니다. R1과 Q1의 접합 커패시턴스 CGS와 CGD는 함께 RC 네트워크를 형성합니다. 커패시터의 충전 및 방전은 스위칭 튜브의 스위칭 속도에 직접적인 영향을 미칩니다. R1이 너무 작으면 쉽게 진동을 일으키고 전자기 간섭이 커지고 R1이 너무 크면 스위치 튜브의 스위칭 속도가 느려집니다. Z1은 일반적으로 MOS 튜브의 GS 전압을 18V 미만으로 제한하여 MOS 튜브를 보호합니다. Q1의 게이트 제어 전압은 톱 모양의 파동입니다. 듀티 사이클이 클수록 Q1의 전도 시간이 길어지고 변압기에 저장된 에너지가 더 많아집니다. Q1이 꺼지면 변압기는 D1, D2, R5 , R4 및 C3를 통과하여 에너지를 방출하고 동시에 자기장 리셋의 목적을 달성하여 다음 에너지 저장 및 전송을 위해 변압기를 준비합니다. IC는 출력 전압 및 전류에 따라 핀 톱형 파의 듀티 사이클을 지속적으로 조정하여 전체 기계의 출력 전류 및 전압을 안정화합니다. C4와 R6는 스파이크 전압 흡수 회로입니다.

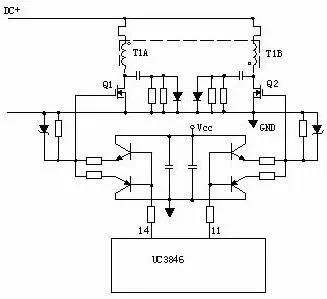

3.4 푸시-풀 전력 변환 회로:

Q1과 Q2가 차례로 켜집니다.

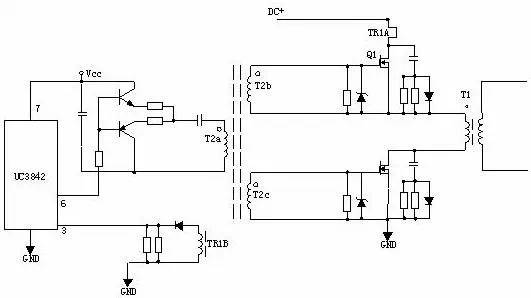

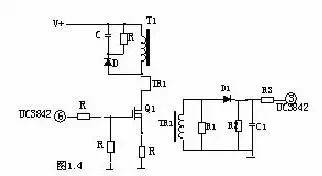

3.5 드라이브 변압기가 있는 전력 변환 회로:

T2는 구동 변압기, T1은 스위칭 변압기, TR1은 전류 루프입니다.

4. 출력 정류기 필터 회로:

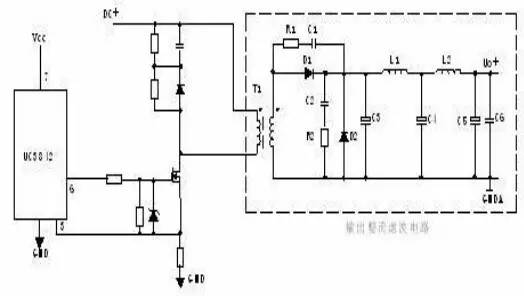

4.1 순방향 정류기 회로:

T1은 1차 극과 2차 극이 같은 위상에 있는 스위칭 변압기입니다. D1은 정류기 다이오드, D2는 프리휠링 다이오드, R1, C1, R2 및 C2는 피크 클리핑 회로입니다. L1은 프리휠링 인덕터이고 C4, L2 및 C5는

π형 필터.

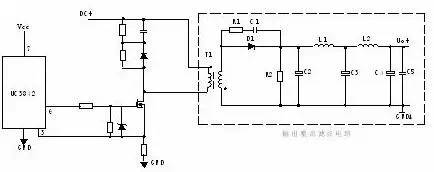

4.2 플라이백 정류기 회로:

T1은 1차 극과 2차 극이 반대 위상에 있는 스위칭 변압기입니다. D1은 정류기 다이오드, R1 및 C1은 피크 클리핑 회로입니다. L1은 프리휠링 인덕터, R2는 더미 부하, C4, L2 및 C5는

π형 필터.

4.3 동기 정류기 회로:

작동 원리: 변압기의 2차측 상단이 양수이면 전류가 C2, R5, R6 및 R7을 통과하여 Q2를 전도하고 회로가 루프를 형성하며 Q2는 정류기입니다. Q1 게이트는 역 바이어스되어 있기 때문에 차단됩니다. 변압기의 2차측 하단이 양극이면 전류가 C3, R4 및 R2를 통과하여 Q1을 전도하고 Q1은 프리휠링 튜브입니다. Q2 게이트는 역 바이어스되어 있기 때문에 차단됩니다. L2는 프리휠링 인덕터이고 C6, L1 및 C7은

π형 필터. R1, C1, R9, C4는 피크 클리핑 회로입니다.

5. 전압 안정화 루프의 원리

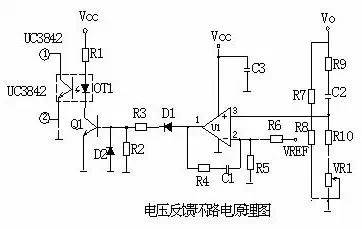

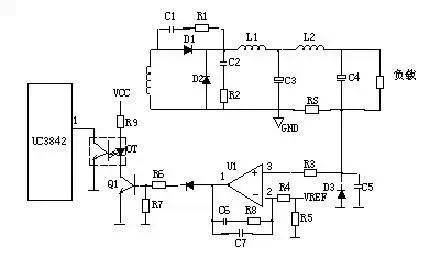

5.1 피드백 회로 개략도:

5.2 작동 원리:

출력 U0이 상승하면 샘플링 저항 R7, R8, R10 및 VR1로 나뉘어 U1③ 핀 전압이 상승합니다. U1② 핀 레퍼런스 전압을 초과하면 U1① 핀이 높은 레벨로 출력되어 Q1이 전도되고 옵토커플러 OT1이 빛을 방출합니다. 다이오드가 빛을 방출하면 광 트랜지스터가 켜지고 그에 따라 UC3842 핀 ①의 전위가 낮아져 U1 ⑥ 핀의 출력 듀티 사이클이 변경되고 U0이 감소합니다. 출력 U0이 감소하면 U1③ 핀 전압이 감소합니다. U1② 핀 레퍼런스 전압보다 낮으면 U1① 핀이 낮은 레벨로 출력되고 Q1이 전도되지 않으며 옵토커플러 OT1 발광 다이오드가 빛을 방출하지 않고 포토 트랜지스터가 전도되지 않으며 UC3842① 핀 전위가 상승합니다. 높아져 U1⑥ 핀 출력 듀티 사이클이 증가하고 U0이 감소합니다. 이를 반복하면 출력 전압이 안정적으로 유지됩니다. VR1을 조정하면 출력 전압 값을 변경할 수 있습니다.

피드백 루프는 스위칭 전원 공급 장치의 안정성에 영향을 미치는 중요한 회로입니다. 예를 들어 피드백 저항 커패시터에 오류, 누설 또는 약한 납땜이 있는 경우 자체 여기 발진이 발생합니다. 결함 현상에는 비정상 파형, 빈 및 완전 부하 진동, 불안정한 출력 전압 등이 포함됩니다.

6. 단락 보호 회로

1. 출력 단자에 단락이 발생한 경우 PWM 제어 회로가 출력 전류를 안전한 범위 내에서 제한할 수 있습니다. 전류 제한 회로를 구현하기 위해 다양한 방법을 사용할 수 있습니다. 단락 시 전력 전류 제한이 작동하지 않으면 다른 회로를 추가하세요.

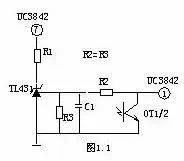

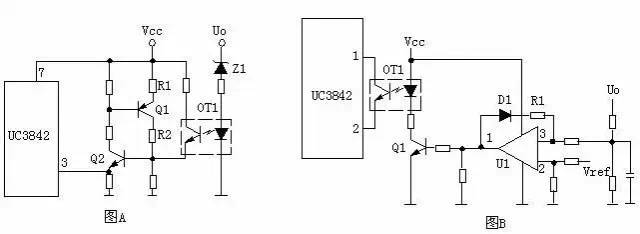

2. 일반적으로 두 가지 유형의 단락 보호 회로가 있습니다. 아래 그림은 저전력 단락 보호 회로를 보여줍니다. 그 원리는 다음과 같이 간략하게 설명되어 있습니다:

출력 회로가 단락되면 출력 전압이 사라지고 옵토커플러 OT1이 전도되지 않으며 UC3842 핀 ①의 전압이 약 5V로 상승하고 R1과 R2의 분할 전압이 TL431 기준을 초과하여 전도되고 UC3842 핀 ⑦의 VCC 전위가 내려가고 IC가 작동을 멈춥니다. UC3842가 작동을 멈춘 후 ① 핀 전위가 사라지고 TL431이 전도되지 않으며 UC3842 ⑦ 핀 전위가 상승하고 UC3842가 재시작되고 사이클이 다시 시작됩니다. 단락이 사라지면 회로가 자동으로 정상 작동 상태로 돌아갈 수 있습니다.

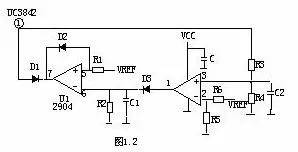

3. 아래 그림은 중전원 단락 보호 회로입니다. 그 원리는 다음과 같이 간략하게 설명되어 있습니다:

출력이 단락되어 UC3842의 ① 핀의 전압이 상승하고 U1의 ③ 핀의 전위가 ② 핀보다 높으면 비교기는 ① 핀을 플립하고 높은 전위를 출력하여 C1을 충전합니다. C1의 양쪽 끝 전압이 핀 ⑤의 기준 전압을 초과하면 U1 ⑦ 핀이 낮은 전위를 출력하고 UC3842의 ① 핀이 1V 이하가 되면 UC3842는 작동을 멈추고 출력 전압은 0V가 되며 사이클이 다시 시작됩니다. 단락이 사라지면 회로가 정상적으로 작동합니다. R2와 C1은 충전 및 방전 시간 상수입니다. 저항 값이 올바르지 않으면 단락 보호 기능이 작동하지 않습니다.

4. 아래 그림은 일반적인 전류 제한 및 단락 보호 회로입니다. 작동 원리는 다음과 같이 간략하게 설명되어 있습니다:

출력 회로가 단락되거나 과전류가 발생하면 트랜스포머의 1차측 전류가 증가하고 R3의 전압 강하가 증가하며 핀 ③의 전압이 증가하고 UC3842의 핀 ⑥의 출력 듀티 사이클이 서서히 증가합니다. 핀 ③의 전압이 1V를 초과하면 UC3842는 꺼지고 출력이 없습니다. .

5. 아래 그림은 변류기를 사용하여 전류를 샘플링하는 보호 회로입니다. 전력 소비는 낮지만 비용이 높고 회로가 복잡합니다. 작동 원리는 다음과 같이 간략하게 설명합니다:

출력 회로가 단락되거나 전류가 너무 크면 TR1의 2차 코일에 의해 유도되는 전압이 높아집니다. UC3842의 ③ 핀이 1볼트를 초과하면 UC3842는 작동을 멈추고 반복해서 시작됩니다. 단락 또는 과부하가 사라지면 회로가 저절로 복구됩니다.

7. 출력 단자 전류 제한 보호

위 그림은 일반적인 출력 전류 제한 보호 회로입니다. 작동 원리를 간단히 설명하면 출력 전류가 너무 크면 RS(망간 구리선) 양쪽 끝의 전압이 상승하고 U1③ 핀 전압이 ② 핀 기준 전압보다 높아집니다. U1① 핀 출력 고전압, Q1이 켜지고 광 커플러에서 광전 효과가 발생하고 UC3842의 핀 1 전압이 감소하고 출력 전압이 감소하여 출력 과부하 전류 제한의 목적을 달성합니다.

8. 출력 과전압 보호 회로의 원리

출력 과전압 보호 회로의 기능은 출력 전압이 설계값을 초과할 때 출력 전압을 안전한 값으로 제한하는 것입니다. 스위칭 전원 공급 장치의 내부 전압 안정화 루프가 고장 나거나 사용자의 부적절한 작동으로 인해 출력 과전압이 발생하면 과전압 보호 회로가 다운스트림 전기 장비가 손상되지 않도록 보호합니다. 가장 일반적으로 사용되는 과전압 보호 회로는 다음과 같습니다:

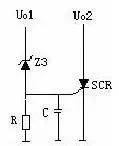

1. SCR 트리거 보호 회로:

위 그림과 같이 Uo1의 출력이 상승하면 전압 조정기 튜브(Z3)가 고장 나 켜지고 실리콘 제어 정류기(SCR1)의 제어 단자가 트리거 전압을 가져와 사이리스터가 켜집니다. Uo2 전압이 접지로 단락되면 과전류 보호 회로 또는 단락 보호 회로가 작동하여 전체 전원 회로의 작동을 중지합니다. 출력 과전압 현상이 제거되면 사이리스터의 제어 단자 트리거 전압이 R을 통해 접지로 방전되고 사이리스터가 꺼진 상태로 돌아갑니다.

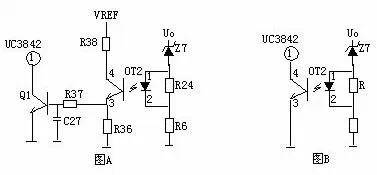

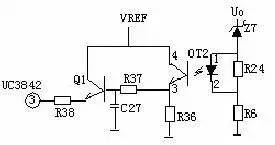

2. 광전 결합 보호 회로:

위 그림과 같이 Uo에 과전압 현상이 발생하면 전압 조정기 튜브가 끊어져 전도되고 전류가 옵토커플러(OT2) R6을 통해 접지로 흐릅니다. 옵토커플러의 발광 다이오드가 빛을 방출하여 옵토커플러의 포토 트랜지스터가 통과하게 됩니다. Q1의 베이스는 전기 전도성이며 3842의 ③ 핀의 전압이 감소하여 IC가 꺼지고 전체 전원 공급 장치의 작동이 중지됩니다. Uo는 0이고 사이클이 반복됩니다.

3. 출력 전압 제한 보호 회로:

출력 전압 제한 보호 회로는 아래와 같습니다. 출력 전압이 상승하면 전압 레귤레이터 튜브가 켜지고 옵토커플러가 켜집니다. Q1의 베이스에 구동 전압이 있고 채널이 연결됩니다. UC3842③의 전압이 증가하면 출력이 감소하고 전압 레귤레이터 튜브가 전도하지 않습니다. UC3842③ 전압이 감소하면 출력 전압이 증가합니다. 이를 반복하면 출력 전압은 전압 레귤레이터 튜브의 전압 조절 값에 따라 일정 범위 내에서 안정화됩니다.

4. 출력 과전압 차단 회로:

그림 A의 작동 원리는 출력 전압 Uo가 증가하면 전압 조정기 튜브가 켜지고 옵토커플러가 켜지며 Q2의 베이스가 전기 전도성을 갖는다는 것입니다. Q2의 전도로 인해 Q1의 베이스 전압이 감소하고 또한 켜집니다. Vcc 전압이 R1, Q1, R2를 통과하면 Q2는 항상 전도성을 가지게 되고 UC3842의 ③ 핀은 항상 높은 레벨로 유지되어 작동을 멈춥니다. 그림 B에서는 UO가 상승하면 U1 ③ 핀의 전압이 상승하고 ① 핀이 높은 레벨로 출력됩니다. D1과 R1이 존재하기 때문에 U1 ① 핀은 항상 높은 레벨을 출력합니다. Q1은 항상 켜져 있습니다. UC3842 ① 핀은 항상 로우 레벨이며 작동을 멈춥니다. . 긍정적 피드백?

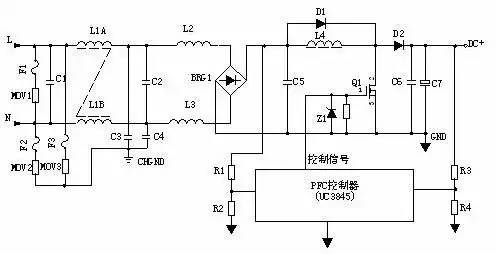

9. 역률 보정 회로(PFC)

1. 원리 다이어그램:

2. 작동 원리:

입력 전압은 L1, L2, L3 등으로 구성된 EMI 필터를 통과하고 BRG1이 한 경로를 정류하여 PFC 인덕터로 보냅니다. 다른 경로는 R1과 R2로 나누어 입력 전압의 샘플로 PFC 컨트롤러로 보내 제어 신호의 듀티를 조정합니다. 비율, 즉 Q1의 온/오프 시간을 변경하여 PFC 출력 전압을 안정화합니다. L4는 Q1이 켜져 있을 때 에너지를 저장하고 Q1이 꺼져 있을 때 에너지를 방출하는 PFC 인덕터입니다. D1은 스타트업 다이오드입니다. D2는 PFC 정류기 다이오드, C6 및 C7 필터입니다. PFC 전압의 한 채널은 다운스트림 회로로 전송되고 다른 채널은 R3 및 R4로 나눈 다음 제어 신호의 듀티 사이클을 조정하고 PFC 출력 전압을 안정화하기 위해 PFC 출력 전압의 샘플로 PFC 컨트롤러로 전송됩니다.

10. 입력 과전압 및 저전압 보호

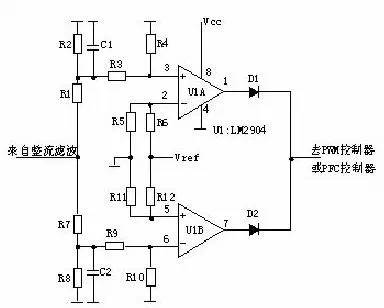

1. 회로도:

2. 작동 원리:

AC 입력 및 DC 입력 스위칭 파워 서플라이의 입력 과전압 및 저전압 보호 원리는 거의 동일합니다. 보호 회로의 샘플링 전압은 입력 필터링된 전압에서 나옵니다. 샘플링 전압은 두 개의 채널로 나뉩니다. 한 채널은 R1, R2, R3 및 R4로 나눈 다음 비교기 핀 3에 입력됩니다. 샘플링 전압이 핀 2의 기준 전압보다 높으면 비교기 핀 1이 높은 레벨을 출력하여 메인 컨트롤러를 제어하여 전원 공급 장치를 종료하고 출력이 없습니다. 다른 채널은 R7, R8, R9, R10으로 나눈 다음 비교기 핀 6에 입력됩니다. 샘플링 전압이 핀 5의 레퍼런스 전압보다 낮으면 비교기 핀 7이 높은 레벨을 출력하여 메인 컨트롤러를 종료하도록 제어하고 전원 공급 장치에는 출력이 없습니다.